# PROGRAMMING NAND FLASH MEMORIES USING ELNEC DEVICE PROGRAMMERS

**Application note**

#### Disclaimer:

This application note describes how to program NAND flash devices using Elnec device programmers. Before reading this document, user should be familiarized with NAND flash devices. There are plentiful sources available through the web containing detailed informations about NAND flash internal organization, errors in NAND flash, basic algorithms, etc. Study, please, your device datasheet thoroughly, at least.

This application note is provided by our technical support department to help our customers and is provided "as-is", without warranty of any kind, either expressed or implied. We reserve the rights to make changes to the information available in this application note at any time and assume no liability for applications assistance, customer product design and any damages arising from the use of this application note.

This application note may refer to various products and brand names that may be claimed as property of their respective owners.

Version 1.1/08.2021 Page 2 of 85

## **CONTENTS**

| 1. BRIEF COMMENTS ON NAND FLASH INWARDS                             | 9  |

|---------------------------------------------------------------------|----|

| 2. BRIEF COMMENTS ON INVALID BLOCKS                                 | 12 |

| 3. BRIEF COMMENTS ON BIT ERRORS                                     | 13 |

| 4. TWO FACTORS THAT PROGRAMMER RELIES ON                            | 14 |

| 5. DATA ORGANIZATION IN PG4UW CONTROL SOFTWARE BUFFER               | 15 |

| 6. LOADING DATA INTO PG4UW CONTROL SOFTWARE BUFFER                  | 16 |

| 6.1. LOADING MULTIPLE DATA IMAGES                                   | 17 |

| 7. ACCESS METHOD WINDOW                                             | 18 |

| 7.1. Invalid Block Management                                       | 19 |

| 7.1.1. Treat All Blocks                                             | 19 |

| 7.1.2. Skip IB                                                      | 20 |

| 7.1.3. Skip IB with map in 0-th block                               | 21 |

| 7.1.4. Skip IB with excess abandon                                  | 22 |

| 7.1.5. RBA (Reserved Block Area)                                    | 22 |

| 7.1.6. Check IB without access                                      | 25 |

| 7.1.7. Check IB with Skip IB                                        | 25 |

| 7.1.8. Discard Invalid block(s) data                                | 25 |

| 7.1.9. Multiple partitions with Skip IB                             | 26 |

| 7.1.9.1. Partition definition file                                  |    |

| 7.1.9.1.1. Qualcomm multiply partition format (*.mbn)               |    |

| 7.1.9.1.1.1 Procedure for two input files                           |    |

| 7.1.9.1.1.2. Procedure for single input file                        |    |

| 7.1.9.1.2. Comma separated values format (*.csv)                    |    |

| 7.1.9.1.3. Group define format (*.def)                              | 30 |

| 7.1.9.1.4. Loading Partition definition file                        |    |

| 7.1.9.1.4.1. Error codes on Partition definition file load          | 33 |

| 7.1.9.2. Access Method window options validity in partitioning mode | 33 |

| 7.1.9.3. Safe working procedure                                     |    |

| 7.1.10. Linux MTD compatible                                        |    |

| 7.1.11. Redirection with HW Look Up Table (LUT)                     |    |

| 7.2. Spare area usage                                               | 35 |

| 7.2.1. Do not use                                                          | 35 |

|----------------------------------------------------------------------------|----|

| 7.2.2. User data                                                           | 35 |

| 7.2.3. User data with IB info forced                                       | 35 |

| 7.2.4. ECC – Hamming (by Samsung)                                          | 36 |

| 7.2.5. ECC – Hamming (2×256 byte frame) variant 1 and 2                    | 37 |

| 7.3. DEVICE INTERNAL ECC CONTROLLER OPTIONS                                | 40 |

| 7.3.1. Enable device internal ECC controller                               | 40 |

| 7.4. USER AREA OPTIONS                                                     | 40 |

| 7.4.1. User Area – Start Block                                             | 41 |

| 7.4.2. User Area – Number of Blocks                                        | 41 |

| 7.4.3. User Area – Last Block                                              | 41 |

| 7.4.4. User Area – Max. Allowed Number of Invalid Blocks in Device         | 41 |

| 7.5. REQUIRED VALID BLOCKS AREA OPTIONS                                    | 42 |

| 7.5.1. Check Required Valid Blocks Area                                    | 42 |

| 7.5.2. Required Valid Blocks Area – Start Block                            | 42 |

| 7.5.3. Required Valid Blocks Area – Number of Blocks                       | 43 |

| 7.6. MAX. ALLOWED NUMBER OF INVALID BLOCKS IN DEVICE OPTIONS               | 43 |

| 7.6.1. Check Max. Allowed Number of Invalid Blocks in Device               | 43 |

| 7.6.2. Max. Allowed Number of Invalid Blocks in Device                     | 43 |

| 7.7. BEHAVIOUR ON NEW INVALID BLOCK OPTIONS                                | 44 |

| 7.7.1. If new invalid blocks is developed                                  | 44 |

| 7.8. TOLERANT VERIFICATION OPTIONS                                         | 44 |

| 7.8.1. Use Tolerant Verify feature                                         | 45 |

| 7.8.2. ECC frame size                                                      | 45 |

| 7.8.3. Acceptable number of errors                                         | 45 |

| 7.8.4. Tolerant verify examples                                            | 45 |

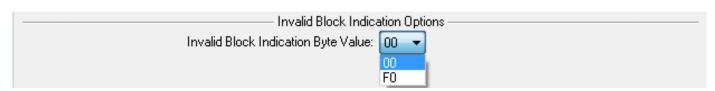

| 7.9. INVALID BLOCK INDICATION OPTIONS (SIMPLIFIED VERSION)                 | 46 |

| 7.9.1. Invalid Block Indication Byte Value                                 | 46 |

| 7.10. Invalid Block Indication options (extended version)                  | 47 |

| 7.10.1. Use customized invalid blocks indication scheme                    | 48 |

| 7.10.2. Alternative block validity indication byte value for invalid block | 48 |

| 7.10.3. Alternative block validity indication byte value for good block    | 48 |

| 7.10.4. Block validity indication byte offset on a page                    | 49 |

| 7.10.5. Pages for block validity indication                                | 49 |

| 7.10.6. Fill invalid block with predefined value                           | 49 |

| 7.10.7. Invalid block filling value                                        | 49 |

| 7.11. RESERVED BLOCK AREA OPTIONS                                          | 50 |

| 7.11.1. RBA Table – Start Block                                            | 50 |

| 7.11.2. RBA Table – Number of Blocks                                       | 50 |

| 7.11.3. RBA Table should be located                                        | 50 |

| 7.12. LINUX MTD COMPATIBLE OPTIONS                                         | 51 |

| 7.12.1. Write BBT to device                                       | 51 |

|-------------------------------------------------------------------|----|

| 7.12.2. BBT should be placed                                      | 52 |

| 7.12.3. BBT should be placed starting from                        | 52 |

| 7.12.4. Number of blocks reserved for BBT                         | 52 |

| 7.12.5. PAGE numbers where BBT should be placed                   | 52 |

| 7.12.6. Page numbers where Mirror BBT should be placed            | 53 |

| 7.12.7. BBT should be stored                                      | 53 |

| 7.12.8. Store BBT version counter                                 | 53 |

| 7.12.9. BBT version counter Value                                 | 53 |

| 7.12.10. Number of bits used per block in BBT on device           | 53 |

| 7.12.11. Value used for RESERVED blocks marking                   | 54 |

| 7.12.12. Use Smart Media bytes order for ECC                      | 54 |

| 7.12.13. Apply MTD specific ECC on partition data                 | 54 |

| 7.13. SPECIAL DEVICE FEATURES                                     | 54 |

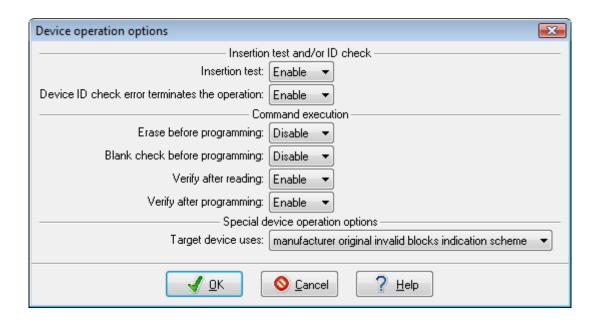

| 8. DEVICE OPERATION OPTIONS WINDOW                                | 56 |

| 8.1. INSERTION TEST AND / OR ID CHECK                             | 57 |

| 8.1.1. Insertion test                                             | 57 |

| 8.1.1.1. Basic test of IC functionality                           | 57 |

| 8.1.2. Device ID check error terminates the operation             | 57 |

| 8.2. COMMAND EXECUTION                                            | 58 |

| 8.2.1. Erase before programming                                   | 58 |

| 8.2.2. Blank check before programming                             | 58 |

| 8.2.3. Verify after reading                                       | 58 |

| 8.2.4. Verify after programming                                   | 59 |

| 8.3. SPECIAL DEVICE OPERATION OPTIONS                             | 59 |

| 8.3.1. Target device uses                                         | 59 |

| 9. SPECIAL NAND FLASH COMMANDS                                    | 60 |

| 9.1. READ ONFI PARAMETER PAGE                                     | 60 |

| 9.2. READ JEDEC PARAMETER PAGE                                    | 63 |

| 9.3. CHECK INVALID BLOCKS                                         | 65 |

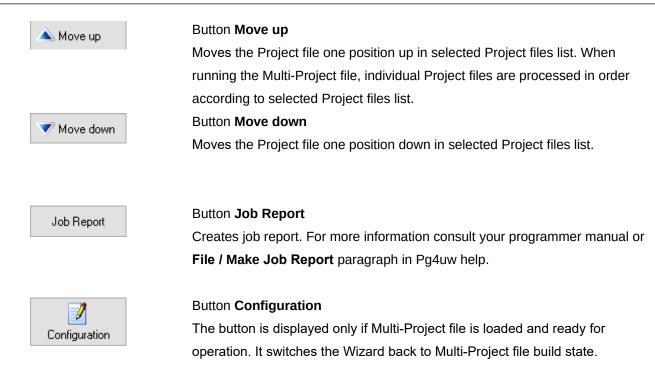

| 10. USING MULTI-PROJECT FEATURE FOR NAND FLASH                    | 66 |

| 10.1. Working with Multi-Project Wizard                           | 66 |

| 10.1.1. Defining the Project files for individual NAND partitions | 68 |

| 10.1.2. Building the Multi-Project file                           | 69 |

| 10.1.3. Running the multi-chip device operation                   | 69 |

| 11. CUSTOMIZED NAND FLASH SUPPORT                                 | 70 |

| 11.1. PARTITIONING SCHEME                                         | 70 |

| 11.2. Invalid blocks management scheme                            | 70 |

| 11.3. DYNAMIC META-DATA SCHEME                                    | 71 |

| 11.4. Page arrangement scheme                                     | 71 |

| 11.5. ERROR CONTROL AND CORRECTION SCHEME                                               | 71                 |

|-----------------------------------------------------------------------------------------|--------------------|

| 11.6. Unused blocks formatting scheme                                                   | 72                 |

| 11.7. INPUT DATA FILE SCHEME                                                            | 72                 |

| 12. FREQUENTLY ASKED QUESTIONS                                                          | 73                 |

| 12.1. Device / Buffer conversions                                                       | 73                 |

| 12.1.1. Conversion of the device offset to the block number                             | 73                 |

| 12.1.2. Conversion of the device offset to the buffer offset                            | 73                 |

| 12.1.3. Conversion of the file size to the blocks count                                 | 74                 |

| 12.1.4. Conversion of the block number to buffer offset                                 | 75                 |

| 12.2. COPYING NAND FLASH MEMORY                                                         | 76                 |

| 12.3. PROBLEMS WITH TOO MANY INVALID BLOCKS                                             | 77                 |

| 12.3.1. How does your programmer identify invalid blocks?                               | 77                 |

| 12.3.2. When working with device, programmer reports tens (hundreds, thousands) of inva | alid blocks. Is it |

| normal?                                                                                 | 77                 |

| 12.3.3. I have made a lot of invalid blocks in my device. Can I fix it somehow?         | 77                 |

| 12.4. COMMAND EXECUTION DILEMMAS                                                        | 78                 |

| 12.4.1. Erase before programming                                                        | 78                 |

| 12.4.2. Blank check before programming                                                  | 78                 |

| 12.4.3. Verify after programming                                                        | 78                 |

| 12.4.4. Pg4uw software recommends me to set more User Area blocks than I have set, sa   | ying it is more    |

| effective. Is it OK?                                                                    | 78                 |

| 13. APPENDIX A: ERRORS IN NAND FLASH – THE BACKGROUND                                   | 79                 |

| 13.1. Memory wear (endurance) errors                                                    | 79                 |

| 13.2. READ DISTURB ERRORS                                                               |                    |

| 13.3. PROGRAM DISTURB ERRORS                                                            | 81                 |

| 13.4. Over-programming errors                                                           | 82                 |

| 13.5. Data retention errors                                                             | 83                 |

|                                                                                         |                    |

## LIST OF FIGURES

| Figure 1: NAND flash vs. NOR flash cell comparison                                    | 9  |

|---------------------------------------------------------------------------------------|----|

| Figure 2: NAND flash internal structure                                               | 10 |

| Figure 3: Invalid Block Map building flowchart                                        | 12 |

| Figure 4: Buffer data layout, if spare area is not used                               | 15 |

| Figure 5: Buffer data layout, if spare area is used                                   | 15 |

| Figure 6: Load file dialog window                                                     | 16 |

| Figure 7: Invalid Block Management options                                            | 19 |

| Figure 8: Treat All Blocks technique graphic representation                           | 20 |

| Figure 9: Skip IB technique graphic representation                                    | 21 |

| Figure 10: Device layout depending of RBA Table should be located option value        | 23 |

| Figure 11: RBA technique graphic representation                                       | 23 |

| Figure 12: Multiple partitions with Skip IB technique graphic representation          | 27 |

| Figure 13: Load partition table window                                                | 31 |

| Figure 14: Example of partition table stored in buffer                                | 31 |

| Figure 15: Successful partition definition file load listing example in log window    | 32 |

| Figure 16: Spare area usage options                                                   | 35 |

| Figure 17: ECC - Hamming (by Samsung) page segmentation example                       | 36 |

| Figure 18: ECC Hamming (by Samsung) spare area layout for small page (512+16 bytes)   | 36 |

| Figure 19: ECC Hamming (by Samsung) spare area layout for large page (2 048+64 bytes) | 36 |

| Figure 20: Device internal ECC controller options                                     | 40 |

| Figure 21: User Area options                                                          | 40 |

| Figure 22: Required valid blocks area options                                         | 42 |

| Figure 23: Max. allowed number of blocks in device options                            | 43 |

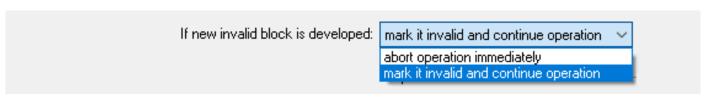

| Figure 24: Behaviour on new invalid block options                                     | 44 |

| Figure 25: Tolerant verification options                                              | 45 |

| Figure 26: Invalid block indication options (simplified version)                      | 46 |

| Figure 27: Invalid blocks indication options (extended version)                       | 48 |

| Figure 28: Reserved blocks area options                                               | 50 |

| Figure 29: Linux MTD compatible options                                               | 51 |

| Figure 30: Special device features menu example                                       | 54 |

| Figure 31: Insertion test and ID check options                                        | 57 |

| Figure 32: Command execution options                                                  | 58 |

| Figure 33: Special device operation options                                           | 59 |

## AN: Programming NAND flash memories using Elnec device programmers

| Figure 34: | Menu device                                                | 60 |

|------------|------------------------------------------------------------|----|

| Figure 35: | Empty Pg4uw Multi-Project Wizard window                    | 66 |

| Figure 36: | Multi-Project Wizard window with Multi-Project file loaded | 69 |

| Figure 37: | A NAND flash block architecture                            | 79 |

| Figure 38: | Wear-out (endurance) errors                                | 80 |

| Figure 39: | Read disturb errors                                        | 81 |

| Figure 40: | Program disturb errors                                     | 82 |

| Figure 41: | Over-programming errors                                    | 83 |

| Figure 42. | Data retention errors                                      | 84 |

#### 1. Brief comments on NAND flash inwards

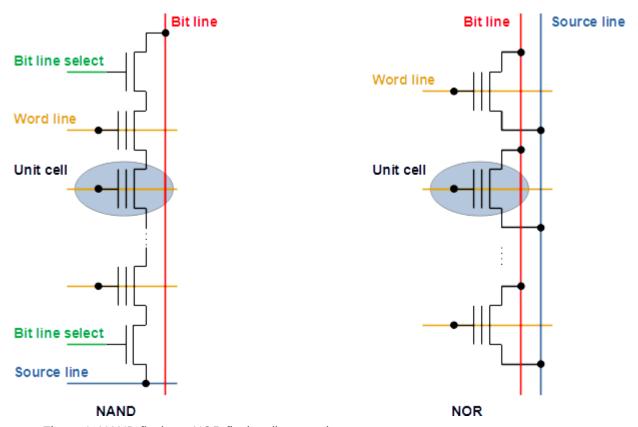

• NOR flash and NAND flash **cell difference** (see Figure 1):

In **NOR flash**, each cell has one end connected directly to source line (ground), and the other end connected directly to a bit line. This arrangement is called NOR flash because it acts like a NOR gate: when one of the word lines is brought high, the corresponding storage transistor acts to pull the output bit line low.

In **NAND** flash the transistors are connected in a way that resembles a NAND gate: several transistors are connected in series, and the bit line is pulled low only if all the word lines are pulled high. These groups are then connected via some additional transistors to a NOR-style bit line array in the same way that single transistors are linked in NOR flash.

Figure 1: NAND flash vs. NOR flash cell comparison.

• SLC, MLC, TLC, QLC...: These maginc acronyms stand for x-Level Cell technology. Theirs usage is, however, rather confusing. Single Level Cell (SLC) uses 2 levels of electric charge to store 1 bit of information (0 or 1). Multi Level Cell (MLC) uses 4 levels of electric charge to store 2 bits of information (00, 01, 10, 11). Triple Level Cell (TLC) uses 8 levels of electric charge to store 3 bits of information (000, 001,

Version 1.1/08.2021 Page 9 of 85

- 010, 011, 100, 101, 110, 111). And finally Quad Level Cell (QLC) uses 16 levels of electric charge to store 4 bits of information. Converting of electric charge level to corresponding logic level is quite a difficult task, so with increasing number of levels, the complexity of the converters increases, as well as the error rate.

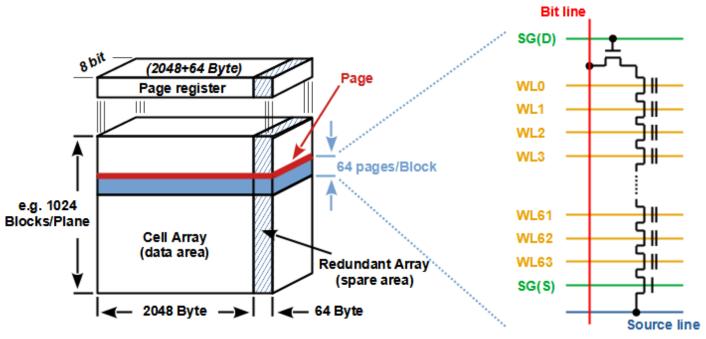

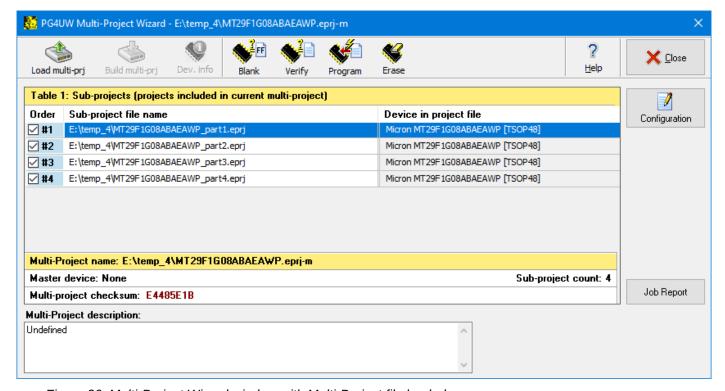

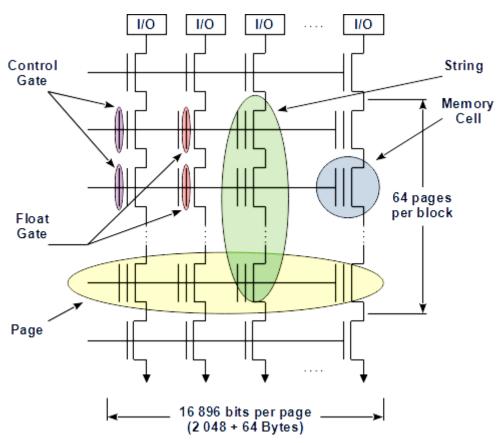

- NAND flash internal structure (see Figure 2): The hierarchical structure of NAND Flash starts at a cell level which establishes strings, then pages, blocks, planes and ultimately a die. A string is a series of connected NAND cells in which the source of one cell is connected to the drain of the next one. Depending on the NAND technology, a string typically consists of 32 to 128 NAND cells. Strings are organised into pages which are then organised into blocks in which each string is connected to a separate line called a bit line. All cells with the same position in the string are connected through the control gates by a word line. A plane contains a certain number of blocks that are connected through the same bit line. A flash die consists of one or more planes, and the peripheral circuitry that is necessary to perform all the read / write / erase operations.

Figure 2: NAND flash internal structure.

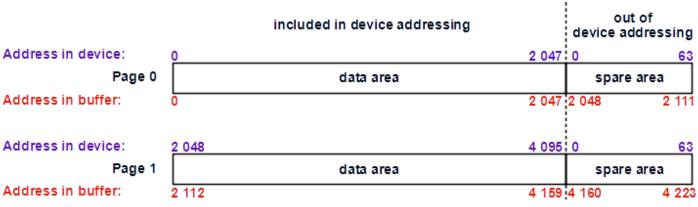

- A NAND flash page consists of data area and spare area (in various sources may be referred also as

"redundant" or "out-of-boundary (OOB)" area). Typically, the data area is used to store a payload data, while

the spare area stores NAND flash management related data ECC checksums, logical block / page

numbers, usage counters, etc.

- Erasing NAND flash: Flash memory allows only two states erased and non-erased. Particular bit of data can be written only if the media is in erased state. Once written, the bit is considered not usable for other write operation. Write operation on flash device can be accomplished only on erased units, so a write operation must be preceded by an erase operation. Only erase operation can revert programmed cells to erased state. During the erase, all cells on a bit string (see Figure 2) are erased, forming a huge block of flash so called erase block. As a result, it is not possible to erase single cell in flash array. During the erasing, the ready / busy signal (R/B# pin or ready / busy flag in STATUS register) is low to indicate that the

Version 1.1/08.2021 Page 10 of 85

device is in busy state. At the end of erase process, all cells in a block are checked if they are in erased state and the result is reported via pass / fail flag in STATUS register.

- Programming NAND flash: NAND flash devices are programmed on a page-by-page basis. A page is written

into page register and then programmed into memory array. During the programming, the ready / busy signal

(R/B# pin or ready / busy bit in STATUS register) is low to indicate that the device is in busy state. At the end

of programming process, all bits on a page expected to be programmed to 0 are checked and the result is

reported in pass / fail flag in STATUS register.

- Reading NAND flash: NAND flash devices are read on a page-by-page basis. Bits in a flash cell array are read by changing the voltage on rows and columns of cells followed by accessing the results. A page is moved from flash cell array into page register. During a page preparation, the ready / busy signal (R/B# pin or ready / busy bit in STATUS register) is low to indicate that the device is in busy state. After the page is ready, data can be lifted out of the device.

Version 1.1/08.2021 Page 11 of 85

## 2. BRIEF COMMENTS ON INVALID BLOCKS

- Invalid block (in various sources may be referred also as "bad block" or "damaged block") is a block that contains

one or more permanently damaged memory cells.

- Presence of invalid block(s) does not affect the function of other blocks in device.

- There may be invalid blocks yet in new (not used before) device. Other invalid blocks may develop over time.

- Invalid block should not be used for programming data may be lost.

- Invalid block should not be erased information about its invalidity may be lost.

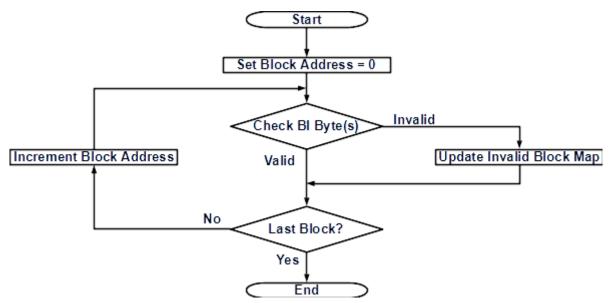

- There is BI byte somewhere in a block. Its location is specified by device manufacturer. For SLC devices, it is typically in first spare area byte within first and / or second page in a block. For MLC devices, it is typically in first spare area byte within first and / or last page in a block. But other locations are also used.

- Before any operation with device, all blocks must be screened for BI bytes values. This process is so-called Invalid block map building. Typical flowchart:

Figure 3: Invalid Block Map building flowchart.

- There are software techniques generally called invalid blocks management used for treatment of existing invalid blocks. These techniques are relevant to know before pre-programming NAND flash device.

- There are software techniques generally called wear levelling management used for new invalid blocks development prevention (see <u>Wikipedia</u> for more information). These techniques are used during end-appliance usage and, usually, are not relevant to know before pre-programming NAND flash device.

Version 1.1/08.2021 Page 12 of 85

## 3. BRIEF COMMENTS ON BIT ERRORS

- Typically, bit errors are temporary errors and disappear after erase. Otherwise, respective block must be considered invalid.

- Bit errors are native to NAND flash memories. They can be considered to be a drawback of NAND flash technology. Typically, they occur due to an influence between adjacent memory cells.

- Bit errors may be detected and recovered. Various ECC algorithms are used for this purpose. Typical representatives are Hamming, BCH (Bose Chaudhuri Hocquenghem) and RS (Reed Solomon) algorithms (see Wikipedia for more information on <u>Hamming</u>, <u>BCH</u> and <u>RS</u>).

- Individual ECC algorithms may be distinguished using several basic characteristics: the frame size (a number of bytes / words covered by single application of the algorithm), the strength (a number of bit errors that can be recovered in the frame of specified size) and the number of control bits / bytes (a size of overhead data).

- For each NAND flash device, the manufacturer specifies required minimum ECC parameters (e.g. 4 bit errors recovery in 512 bytes frame). At least, an ECC algorithm capable to recover specified number of bit errors over specified frame size must be used.

- Our programmers can support selected ECC algorithms. In addition, we offer customized implementations that

may support any ECC algorithm specified by customer. Also, a generalized solution is available on verify, the

programmer may accept specified number of bit errors in specified number of bytes and suppose, that these bit

errors will be corrected by ECC algorithm in real application see chapter Tolerant verification options.

See chapter Errors in NAND flash - the background for detailed information about NAND flash errors origin.

Version 1.1/08.2021 Page 13 of 85

#### 4. Two factors that programmer relies on

- The user: Programmer will do only what user has ordered to do. Programmer can detect device boundary

exceeding, but cannot foretell e.g. a block from where data should start. Please, do not rely on default settings.

Those are just some general preferences originating from device parameters and algorithm simplifying rather

than from your particular needs.

- NAND flash device internal controller: The controller communicates with programmer via STATUS register. On erase, the controller checks if all memory cells in a block are in erased state. If controller says that the block is erased properly, programmer will rely on this information none (significant time consuming) blank check is performed after erase. If controller says that the block is not erased properly, programmer will consider that block invalid the block is treated regarding to selected invalid block management. On programming, the controller checks if all page locations expected to be in 0 are really in 0. If controller says that the page is programmed properly, programmer will continue with next page. If controller says that the page is not programmed properly, programmer will consider related block invalid the block is treated regarding to selected invalid block management.

Version 1.1/08.2021 Page 14 of 85

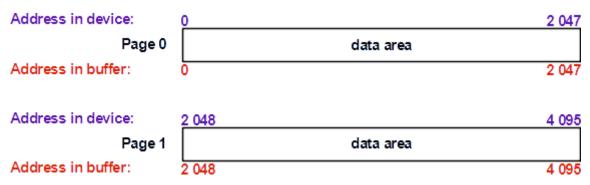

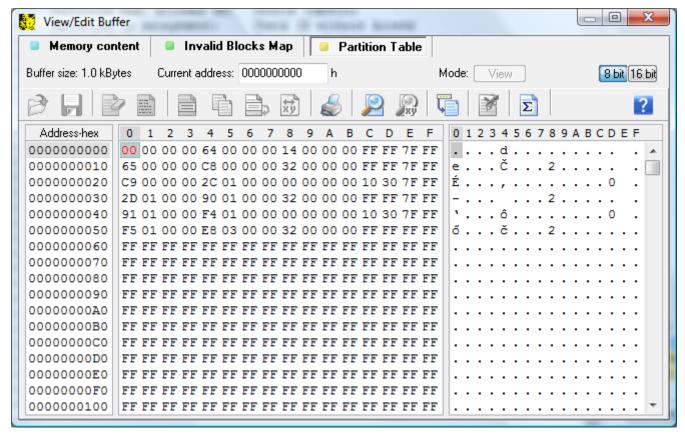

## 5. Data organization in pg4uw control software buffer

Data are stored in buffer as a continuous sequence of pages. Please, be aware of fact, that page spare area is not included in normal device addressing. Control software buffer, however, uses linear addressing. This may lead to hazardous misunderstandings resulting in incorrect data positioning in device. Compare, please, following pictures:

Figure 4: Buffer data layout, if spare area is not used.

Figure 5: Buffer data layout, if spare area is used.

Considering a common NAND flash device with 2 048 + 64 bytes in a page and 64 pages in a block, the first byte of second block in device will be addressed using offset 2 0000h in device, but using offset 2 1000h in buffer. It is crucial to keep this in mind, especially if working with partitions.

Version 1.1/08.2021 Page 15 of 85

#### 6. LOADING DATA INTO PG4UW CONTROL SOFTWARE BUFFER

Primarily, command **File / Load** (short-cut <F3>) should be used for input image loading into buffer. Software can recognize plentiful data formats, however, for devices with capacity of 16 Gbit and more only raw binary mode (\*.BIN) may be supported.

Figure 6: Load file dialog window.

Data image file should correspond with a copy of NAND flash device free of any invalid blocks. Depending on other settings, it must or must not contain also spare area data. If selected mode requires spare area data and your image does not contain it (relevant mainly for partitioning techniques), you can add blank (all FFh) spare area automatically on image load allowing **Add blank spare area** option (see Figure 6, *Additional operation* panel). It is important to select correct device firstly, since various devices may use different data area and spare area sizes and control software always matches page layout of actually selected device. All other options available in **Load File** window work in their usual way.

Version 1.1/08.2021 Page 16 of 85

#### 6.1. LOADING MULTIPLE DATA IMAGES

If you need to load multiple data image files for single device (relevant mainly for partitioning techniques), you may need to use **Positive offset** option (see Figure 6, *Buffer offset for loading* panel). You may compute the offset using following formula:

positive\_offset = block\_number x pages\_in\_block x page\_size

where:

**block\_number** is the number of target block as is mapped in buffer. Blocks ordering in buffer may differ from their real ordering in device, see buffer to device mapping in chapter dedicated to respective invalid blocks management technique.

pages\_in\_block is the count of pages in one block, as is given in your NAND flash device datasheet.

**page\_size** is the size of a page in bytes or words (for x8 or x16 devices, respectively), as is given in your NAND flash device datasheet. The page size must, or must not include spare area size, depending on other settings.

This way you may load all your data images, file after file, and place them at correct locations in buffer.

Version 1.1/08.2021 Page 17 of 85

## 7. Access method window

| & Access Method                                                       | ×                                             |  |

|-----------------------------------------------------------------------|-----------------------------------------------|--|

| Invalid Block Management:                                             | Skip IB ~                                     |  |

| Spare Area Usage:                                                     | User Data ~                                   |  |

|                                                                       |                                               |  |

| User Area - Start Block:                                              | 000000                                        |  |

| User Area - Number of Blocks:                                         | 002008                                        |  |

| User Area - Last Block:                                               | 002047                                        |  |

| User Area - Max. Allowed Number of Invalid Blocks:                    | 000040                                        |  |

| Check Required Valid Blocks Area                                      |                                               |  |

| Required Valid Blocks Area - Start Block:                             | 000000                                        |  |

| Required Valid Blocks Area - Number of Blocks:                        | 000001                                        |  |

| Check Max. Allowed Number of Invalid Blocks in Device                 |                                               |  |

| Max. Allowed Number of Invalid Blocks in Device:                      | 000040                                        |  |

| mail. Allowed Hamber of Hydrid Diooks in Diones.                      |                                               |  |

| If new invalid block is developed:                                    | mark it invalid and continue operation $\sim$ |  |

| Tolerant Verification                                                 | on Options                                    |  |

| ✓ Use Tolerant Verify feature                                         | on options                                    |  |

| ECC frame size (bytes):                                               | 000512                                        |  |

| Acceptable number of errors:                                          | 000008                                        |  |

| Invalid Block Indica                                                  | tion Options                                  |  |

| Use customized invalid blocks indication scheme                       | aon opaons                                    |  |

| Alternative block validity indication byte value for invalid block:   | 0x00                                          |  |

| Alternative block validity indication byte value for good block:      | 0xFF                                          |  |

| Block validity indication byte offset on a page (0-4319):             | 4096                                          |  |

| Pages for block validity indication (0-63, max. 3 pages):             | 0                                             |  |

|                                                                       |                                               |  |

| Fill invalid block with predefined value Invalid block filling value: | 0x00                                          |  |

|                                                                       |                                               |  |

|                                                                       |                                               |  |

| RBA Table - Start Block:                                              |                                               |  |

| RBA Table - Number of Blocks:                                         | 000015                                        |  |

| RBA Table should be located:                                          | after Block Reservoir V                       |  |

|                                                                       |                                               |  |

| ✓ <u>O</u> K <u>Q</u> ancel <u>P</u> elp                              |                                               |  |

Version 1.1/08.2021 Page 18 of 85

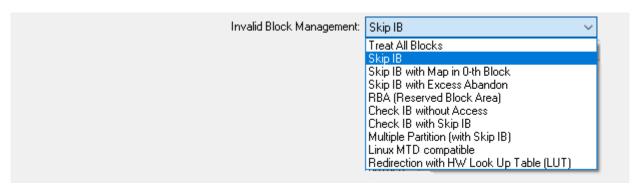

#### 7.1. INVALID BLOCK MANAGEMENT

Our programmers support several general invalid blocks management techniques. Not all techniques described here are supported on all programmers. Any other invalid blocks management technique can be supported upon user's request.

Figure 7: Invalid Block Management options

#### 7.1.1. TREAT ALL BLOCKS

In past, we called this technique "Do not Use", simply because none block validity related decision algorithm is used. All blocks in device are processed identically, not regarding their real validity status.

The technique may be very helpful if dumping unknown data is necessary, e.g. for data recovery from broken USB stick. It allows to create the image comprising all blocks in device for further analysis.

#### Proceed with caution!

Since this technique does not differentiate between valid and invalid blocks, you can suffer a damage!

On programming, programmer will try to write data also to invalid blocks. The operation might fail on verify after programming (if enabled), however, if device is still used in end appliance, it might cause its malfunction.

On erase, programmer will try to erase also invalid blocks. This may damage BI bytes in invalid blocks, so information about their invalidity might be lost. Programmer is rather simple device not capable to perform any reliability tests similar to those one on manufacturing line, so it cannot recover this information.

Using **Treat All Blocks** technique, a number of blocks specified in option **User Area – Number of Blocks** will be taken counting from buffer start, and programmed into device starting from a block specified in option **User Area – Start Block**. The blocks will be programmed in device, not regarding theirs validity. If target block is invalid, data will be lost. The number of blocks specified for processing does not necessarily have to be the same size as the size of data loaded in buffer.

On device read, reciprocally, a number of blocks specified in option **User Area – Number of Blocks** will be read from device starting from a block specified in option **User Area – Start Block**, not taking source blocks validity into account, and stored into buffer counting from buffer start.

Version 1.1/08.2021 Page 19 of 85

Figure 8: Treat All Blocks technique graphic representation.

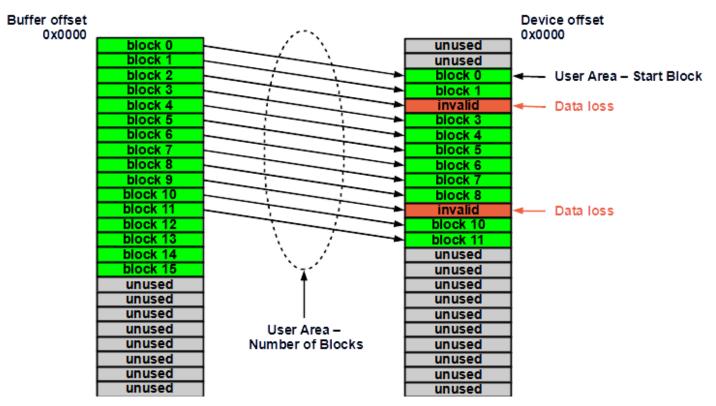

#### 7.1.2. SKIP IB

This is the simplest technique used for treatment of invalid blocks. If target block is invalid, it is skipped and next valid block is used instead. The next data are then programmed into (next+1)-th block. This will produce a shift in data offset. The shift increases with each skipped invalid block. If there are too many invalid blocks in target device area, not all data might be programmed. Excess data would be lost, therefore operation is halted at the first moment when such a condition is recognized (typically on initial Invalid Blocks Map building).

Using **Skip IB** technique, a number of blocks specified in option **User Area – Number of Blocks** will be taken counting from buffer start, and programmed into device starting from a block specified in option **User Area – Start Block**. If target block is invalid, actual data will be programmed into next valid block, thus shifting all next data by offset of one block. The number of blocks specified for processing does not necessarily have to be the same size as the size of data loaded in buffer. If a block specified in option **User Area – Last Block** is reached and not all specified blocks are programmed, operation is halted with error.

On device read, reciprocally, a number of blocks specified in option **User Area – Number of Blocks** will be read from device starting from a block specified in option **User Area – Start Block**. Read data will be stored into buffer counting from buffer start. If source block is invalid, it will be skipped (not processed) and programmer will continue with next valid block. Data are stored in buffer continually, without gaps from invalid blocks, so the same image will be created in buffer not regarding invalid blocks distribution over the device. If a block specified in option **User Area – Last Block** is reached and not all specified blocks are read, operation will close with error.

Version 1.1/08.2021 Page 20 of 85

Figure 9: Skip IB technique graphic representation.

#### 7.1.3. SKIP IB WITH MAP IN 0-TH BLOCK

This technique is for backward compatibility with algorithms developed for old NAND flash devices.

Very first NAND flash memories came without spare area, so it was not possible to store BI byte nor any other validity mark out of payload data. Initial invalid blocks were forced to all zeros state. But after first device programming, it was not possible to distinguish, whether the block is invalid or programmed with all zeros intentionally (e.g. some variables initialization section). One of used solutions consisted in programming Invalid Blocks Map in first device block (block #0000). All other behaviour is the same as for **Skip IB** technique.

The map uses one bit value to store information about one block. Bit 0 of byte 0 corresponds to block #0000, bit 1 of byte 0 corresponds to block #0001, ..., bit 0 of byte 1 corresponds to block #0008, and so on until the device end. If bit value = 1 then corresponding block is invalid.

You can display the same Invalid Blocks Map using menu command **Buffer / View / Edit Buffer** (short-cut <F4>) and then clicking on **Invalid Blocks Map** tab.

Version 1.1/08.2021 Page 21 of 85

#### 7.1.4. SKIP IB WITH EXCESS ABANDON

This technique is very close to basic **Skip IB** technique, too. Recall, please, a possible data loss due to excessive invalid blocks count in specified area. **Skip IB with excess abandon** technique does not generate error if this lossy condition happen. Data that cannot be programmed will be simply abandoned (lost).

This technique may be useful for applications where multiple data copies are used as a mean of error protection. Typical example is a bootloader storage. Another task where this technique may be useful is programming of various file system related headers into unused (padding) blocks. It can process all valid blocks and will not finish with error due to invalid blocks occurrence.

Compared to **Treat All Blocks** technique, **Skip IB with excess abandon** skips invalid blocks, so programmer does not expect any data there and verify operation can still succeed.

#### 7.1.5. RBA (RESERVED BLOCK AREA)

This is an another kind of invalid blocks management technique, based on replacement of invalid blocks.

Using this approach, the device is subdivided into three regions – user data area, reservoir of blocks for replacement of invalid blocks from user data area, and an area reserved for redirection table (sometimes referred also as table of substitutions). Normally, data are programmed into user data area. If target block is invalid, next free valid block from reservoir is used instead. Redirection table is updated by new invalid-valid pair of blocks. Process then continues with next block data and next block in user data area. After programming all required blocks, redirection table is programmed into the area reserved for this purpose. In addition to information about redirected block pairs, the table may also contain other kinds of data, like some identification header, version numbering, device parameters information, etc.

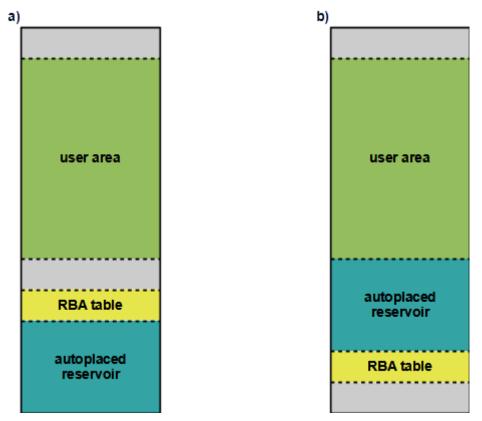

Reserved block area technique, as is implemented in our programmers, is based on Samsung's algorithm and works as is described in following paragraphs. You can exactly specify two areas of three in use – user area, where data should be stored primarily; and RBA Table area, where redirection table should be stored. Reservoir is created automatically, based on setting of option RBA Table should be located, see Figure 10.

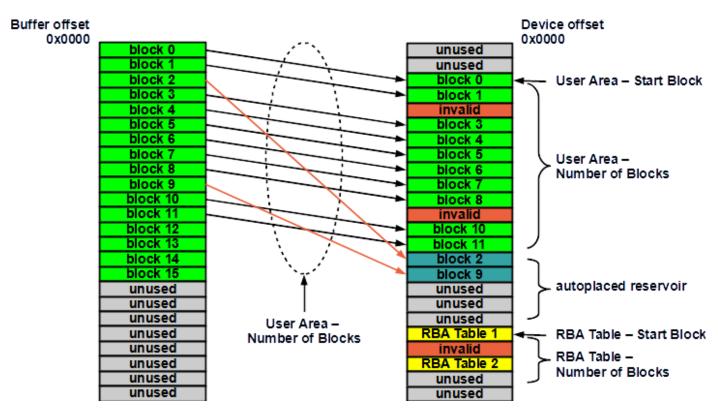

Figure 11 illustrates buffer data to physical blocks assignment on example where RBA Table should be located after reservoir. In the other case, the principle of blocks substitution will be the same, just areas allocation will differ, see Figure 10.

Version 1.1/08.2021 Page 22 of 85

Figure 10: Device layout depending of RBA Table should be located option value: before Block Reservoir (a) and after Block reservoir (b). There may be unused blocks accepted in grey areas.

Figure 11: RBA technique graphic representation.

Version 1.1/08.2021 Page 23 of 85

#### On programming:

A number of blocks specified in option User Area – Number of Blocks will be allocated for user data area, starting from block specified in option User Area – Start Block. Another number of blocks specified in option RBA Table – Number of Blocks will be allocated for redirection table, starting from block specified in option RBA Table – Start Block. If RBA Table should be located = before Block Reservoir, all free blocks between redirection table area and device end will be allocated for block reservoir. If RBA Table should be located = after Block Reservoir, all free blocks between user data area and redirection table area will be allocated for block reservoir.

A number of blocks specified in option **User Area – Number of Blocks** will be taken counting from buffer start and programmed into user data area in device, block by block. If target block is invalid, next free valid block from block reservoir will be used instead. Blocks are picked-up from block reservoir in ascending order (from device start towards device end), invalid blocks are not used. Redirection table in programmer memory will be updated. If there are more invalid blocks in user data area than valid blocks in block reservoir, data loss will occur. In such case, operation will be halted with error.

After programming specified number of data blocks, two copies (original and back-up) of redirection table (RBA Table) will be programmed into redirection table area. **Skip IB** technique is used. If there are less than two valid blocks in redirection table area, those two copies cannot be programmed and operation will be halted with error.

#### On read:

A number of blocks specified in option User Area – Number of Blocks will be allocated for user data area, starting from block specified in option User Area – Start Block. Another number of blocks specified in option RBA Table – Number of Blocks will be allocated for redirection table, starting from block specified in option RBA Table – Start Block. If RBA Table should be located = before Block Reservoir, all free blocks between redirection table area and device end will be allocated for block reservoir. If RBA Table should be located = after Block Reservoir, all free blocks between user data area and redirection table area will be allocated for block reservoir.

Redirection table area will be searched for at least one valid copy of redirection table. If valid redirection table is not found, operation is halted with error.

After successful RBA Table decoding, a number of blocks specified in option **User Area – Number of Blocks** will be read from user data area and stored into buffer counting from buffer start. If source block is listed in redirection table, its substitutive block will be read instead. If it is not possible to read specified number of blocks from user data area + block reservoir, operation will close with error.

#### **Redirection table format:**

RBA Table consists of pages. Each page uses the same data field layout. Each data field is 16 bit wide, stored using little endian format.

The first data field on a page is a header. The header is always of the same value FDFEh.

The second data field on a page is count field. Count field stores page sequence number, counting from 1 for first page of first RBA Table copy and incrementing by one for each other page. For second RBA table copy, the counter continues incrementing (if table uses e.g. 4 pages, count field value for first page of second RBA Table copy will be 5).

Version 1.1/08.2021 Page 24 of 85

Further, a page continues with invalid block – replacement block data field pairs. These pairs store numbers of invalid blocks from user data area and theirs respective substitution blocks from blocks reservoir used for replacement. Single page can hold information about (page data area size – 4) / 4 redirections.

Unused bytes in RBA Table block are set to blank state FFh.

#### 7.1.6. CHECK IB WITHOUT ACCESS

**Check IB without access** technique performs checks with regard to set rules, but does not execute any other device access. For that reason, only programming command is available after confirming this technique. The command is used for running the tests.

This technique may be used to simulate the programming, e.g. if you are going to perform initial programming of the NAND flash device after assembling the end-appliance. In such case you may be interested in not using memories with too much invalid blocks for assembly (thus minimizing the waste due to memory units of poor quality).

An area starting from block specified in option User Area – Start Block up to block specified in option User Area – Last Block is scanned for invalid blocks.

If the count of invalid blocks in that area exceeds a number specified in option **User Area – Max. Allowed Number of Invalid Blocks in Device**, an error is reported.

If the count of valid blocks in that area is less than a number specified in option **User Area – Number of Blocks**, an error is reported.

If enabled, required valid blocks area is checked, see chapter **Required Valid Blocks Area options**.

If enabled, Max. Allowed Number of Invalid Blocks in Device is checked.

#### 7.1.7. CHECK IB WITH SKIP IB

After performing all tests in the same manner as if **Check IB without access** technique has be used, **Skip IB** technique will be used for accessing the device.

This technique may be helpful if you need to guarantee some number of unused valid blocks in user data area. E.g. if you need to program 80 blocks into area of 100 blocks, standard **Skip IB** technique will accept 20 invalid blocks in that area. But using **Check IB with Skip IB** technique, you may allow acceptance of only e.g. 10 invalid blocks. Remaining 10 valid blocks may be used for further invalid blocks replacement during end-appliance lifetime.

### 7.1.8. DISCARD INVALID BLOCK(S) DATA

**Note:** This invalid blocks management technique can be activated only for techniques based on partitioning, and only using \*.CSV partition definition file.

**Discard invalid block(s) data** is a hybrid of **Treat All Blocks** and **Skip IB** techniques. If programmer meets invalid block in device, it simply increases the pointer one block forward in both, device and buffer. Data belonging to invalid block are discarded (ignored).

This technique is intended particularly for programming various bootloaders and data tables, when multiple copies are used as an instrument of error protection.

Version 1.1/08.2021 Page 25 of 85

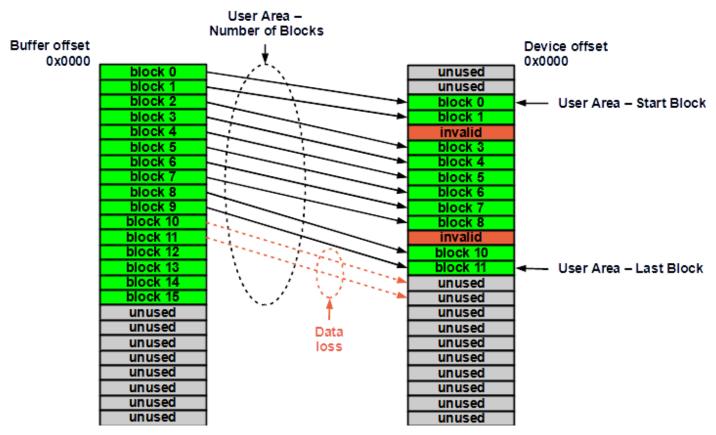

#### 7.1.9. MULTIPLE PARTITIONS WITH SKIP IB

**Note:** This invalid blocks management technique offers wide range of options that were implemented in successive steps. If enabled for discontinued programmers, it is called **Qualcomm Multiple Partition** (historical reason).

In very simple words, this is **Skip IB** technique extended for allowance of multiple user data areas. This comes with variety of new possibilities, but also with more complicated configuration and handling.

User data area is now called **partition**. All user data area settings have respective partition equivalent:

- User Area Start Block → Partition start

- User Area Number of Blocks → Used partition size

- User Area Last Block → Partition end

There are several significant differences from **Skip IB** technique:

- Spare area data are always expected in buffer. If you do not use spare area, you may fill respective areas

by blank data on input image file load by enabling Add blank spare area feature, see chapter Loading data

into pg4uw control software buffer.

- Partition start data in buffer are now expected with the same offset as in device, i.e. **Partition start** value specifies the partition beginning in both, device and buffer.

- Instead of specifying necessary options in Access Method window, partitions are specified via Partition definition file.

- Only some of options available in **Access Method** window will be accepted during operation, see chapter **Access Method window options validity in partitioning mode**.

- Probably, you will need to load several input data images, see chapter Loading multiple data images.

Using **Multiple Partition with Skip IB** technique, programmer will process each partition individually, in increasing order. After programming or reading a partition, the same partition is verified (if enabled). Only after then, if succeeded, the programmer will continue with next partition.

A number of blocks specified by value of **Used partition size** will be taken from buffer counting from a block specified by value of **Partition start**. These data will be programmed into device starting from a block specified by value of **Partition start**, too. If target block is invalid, actual data will be programmed into next valid block, thus shifting all next data by offset of one block. If the block specified by value of **Partition end** is reached and not all specified blocks are programmed, operation is halted with error.

On device read, reciprocally, a number of blocks specified by value of **Used partition size** will be read from device starting from a block specified by value of **Partition start**. Read data will be stored into buffer counting from a block specified by value of **Partition start**, too. If source block is invalid, it will be skipped (not processed) and programmer will continue with next valid block. Data are stored in buffer continually, without gaps from invalid blocks, so the same image will be created in buffer not regarding invalid blocks distribution over the partition. If the block specified by value of **Partition end** is reached and not all specified blocks are read, operation will close with warning.

Version 1.1/08.2021 Page 26 of 85

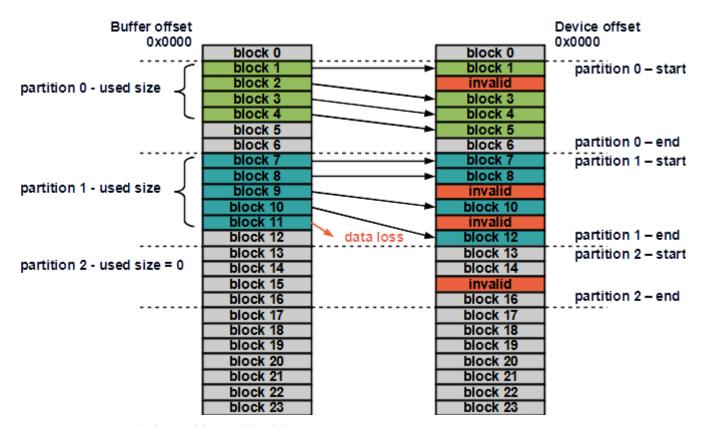

Figure 12 shows an example device with three partitions.

Partition 0 was programmed successfully. Two unused blocks left at partition end (also referred as padding blocks) are enough for compensation of one invalid block found in device.

Partition 1 could not be programmed successfully. There is only one unused block left for invalid blocks compensation, but two invalid blocks were found in device. In consequence, one data block was lost.

Partition 2 is a special kind of unused partition. In fact, it may be used later, by end-appliance itself, but it is not programmed on pre-assembly programming. It may be just specified but not used, simply for your better orientation in more complicated partitioning scheme. Or, there may be other options specified for this partition, providing some level of device quality check (e.g. devices with too many invalid blocks in this partition may be rejected this way from further processing).

Figure 12: Multiple partitions with Skip IB technique graphic representation.

#### 7.1.9.1. PARTITION DEFINITION FILE

Partition definition file is used for instructing the programmer about how to allocate blocks for partitions, and eventually, what further pre- or post-processing apply on partition. There are several different formats supported. All partition definition file formats are described in following chapters.

#### 7.1.9.1.1. QUALCOMM MULTIPLY PARTITION FORMAT (\*.MBN)

**Note:** The support of this format is implemented based only on fragment of specification available from our customer(s). Therefore it cannot be considered full and reliable. If you observe any problems, please, contact our technical support with full MBN file format specification.

Version 1.1/08.2021 Page 27 of 85

Generally, our programmers support two versions of Qualcomm Multiply Partition format. They can be simply distinguished by the number of input files.

#### 7.1.9.1.1.1. Procedure for two input files

If you have two input files available, they are generally named FactoryImage.bin and PartitionTable.mbn.

**PartitionTable.mbn** is rather small (typically 256 bytes) and contains partition table definition. Load this file using menu **File / Load Partition table**, see chapter **Loading Partition definition file**. Actually, the maximum count of supported partitions is 64.

**FactoryImage.bin** may be rather huge and contains binary data image. Load this file using standard **Load** procedure, see chapter **Loading data into pg4uw control software buffer**.

It is possible to save data using this format. To save buffer content in binary format, use standard **Save** procedure (menu **File / Save**, shortcut **<F2>** or Save command from Main toolbar). To save partition table in Qualcomm Multiply Partition compatible format, use menu **File / Save Partition table**.

#### 7.1.9.1.1.2. Procedure for single input file

If you have single input file available, it is generally named FactoryImage2.mbn. The file is rather huge and contains both, partition table definition and binary data image, plus a header. The file can be simply identified using hex-viewer – you must identify text "*Image with header*" at file start.

The header specifies also block validity indication byte position. This parameter is also accepted and used for proper reading and / or verifying the device. The value overwrites manual settings in **Block validity indication byte** offset on a page section of **Access Method** window.

Load this file using standard **Load** procedure, see chapter **Loading data into pg4uw control software buffer**. It is not possible to save data using this format.

#### 7.1.9.1.2. COMMA SEPARATED VALUES FORMAT (\*.CSV)

Partition table definition file uses well-known comma separated values file format.

The file should contain a number of rows corresponding to the number of partitions. Each row specifies one partition.

Values in row should be separated by separator – comma (,) or semicolon (;) may be used. Space characters (ASCII code 20h) are ignored and should not be used in place of values separator.

Each row should contain several values (both, decimal and / or hexadecimal values can be used):

- Partition start (mandatory) specifies the block in device where partition should start. Enter the block number here.

- Partition end (mandatory) specifies the block in device where partition should end. Enter the block number here.

- Used partition size (mandatory) specifies the number of blocks really occupied by partition data. Typically, there are some reserve blocks added for invalid blocks replacement, therefore obviously partition\_end partition\_start > used\_partition\_size. Enter the count of blocks here.

- **Special options** *I* **reserved** (optional / mandatory) this value enables to specify some special options. If you use it just due to comment option usage, enter the value of *FFFFFFFh* here to ensure future compatibility (or *0xFFFFFFFF* whichever form you prefer; keep 4 bytes size).

Version 1.1/08.2021 Page 28 of 85

#### **Special options specification:**

```

MSB (bit 31) LSB (bit 0)

xxxx.xxxx.xxxx.xxxx.xxxx.xxxx.xxxx

```

#### bits 11:0 – Maximum allowed number of invalid blocks in partition:

- FFFh = feature disabled (default)

- any other value specifies the number of invalid blocks that can be accepted in partition

#### bits 15:12 – Invalid blocks management technique:

- 0 = Treat All Blocks

- 1 or Fh = Skip IB (default)

- 2 = Skip IB with excess abandon

- 3 = Check IB without access

- 4 = Discard Invalid block(s) data

Note: It is possible to specify an equivalent of Check IB with Skip IB technique using Skip IB (1h or Fh) technique and non FFFh value for Maximum allowed number of invalid blocks in partition.

bits 22:16 - Reserved for future use, consider 7Fh value for future compatibility.

#### bit 23 - First block in partition must be good:

- 0 = if first block in respective partition is invalid, device is considered bad and operation is aborted

- 1 = feature disabled (default)

#### bits 27:24 - File system preparation:

- Fh = feature disabled (default)

- 0 = JFFS2 Clean Markers are written to unused blocks at respective partition end using MSB byte ordering (big endian)

- 1 = JFFS2 Clean Markers are written to unused blocks at respective partition end using LSB byte ordering (little endian)

bits 31:28 - Reserved for future use, consider Fh value for future compatibility.

**Note:** other values not specified here may be accepted for customized implementations, depending on algorithm specification.

• **Comment** (optional) – you can enter any text here. Primarily, this item is intended for your notes that will help you to orientate in the file. It may contain e.g. partition name. If you use comments, **reserved** option must be also specified.

Version 1.1/08.2021 Page 29 of 85

#### Partition table definition file example:

```

0; 100; 20; 0xff7fffff; boot

101; 200; 50; 0xff7fffff; exec

201; 300; 0; 0xff7f3010; res1

301; 400; 50; 0xff7fffff; fsys

401; 500; 0; 0xff7f3010; res2

501; 1000; 50; 0xffffffff; data

```

For loading the table, use menu File / Load Partition table, see chapter Loading Partition definition file.

It is possible to save your partition table definition using this format. To save partition table data, use menu **File / Save Partition table**. The table is saved using all values in row, a partition number is used for comment.

#### 7.1.9.1.3. GROUP DEFINE FORMAT (\*.DEF)

**Note:** The support of this format is implemented based only on fragment of specification available from customer(s). Therefore it cannot be considered full and reliable. If you observe any problems, please, contact our technical support with full DEF file format specification.

Partition table definition file consists of file header and group records. Each group record specifies one partition.

Load this partition table definition file using menu File / Load Partition table, see chapter Loading Partition definition file.

It is possible to save your partition table definition file using this format. To save partition table data, use menu **File / Save Partition table**.

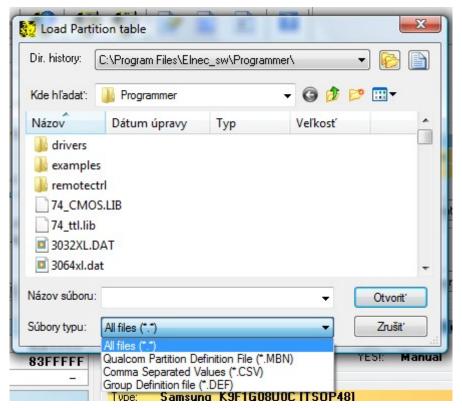

#### 7.1.9.1.4. LOADING PARTITION DEFINITION FILE

Use menu File / Load Partition table to open Load Partition table window. Filter your folder content using partition definition file type mask. Select your file and press button Open.

Your partition definition file is then opened, decoded, checked, listed in log window and stored in special buffer (use menu **Buffer / View / Edit Buffer** to display buffer window, then click on **Partition Table** tab).

Version 1.1/08.2021 Page 30 of 85

Figure 13: Load partition table window.

Figure 14: Example of partition table stored in buffer.

Version 1.1/08.2021 Page 31 of 85

```

Programmer activity log

L0176: >> 17.09.2013, 19:49:28

L0177: Loading file: C:\Program Files\Elnec sw\Programmer\parttable.csv

L0178: File format: Comma Separated Values

L0179: Loading Partition Table...

L0180: Checking Partition Table...

L0181: Checking Partition Table - O.K.

L0182: Partition 0

L0183: Partition start (in blocks): 000000 (0x0000)

L0184: Partition end (in blocks): 000100 (0x0064)

L0185: Partition size (in blocks): 000020 (0x0014)

L0186: Partition IB management:

Skip IB

L0187: Special features:

First block in partition must be good

L0188: Comment:

boot

L0189: Partition 1

L0190: Partition start (in blocks): 000101 (0x0065)

L0191: Partition end (in blocks): 000200 (0x00C8)

L0192: Partition size (in blocks): 000050 (0x0032)

L0193: Partition IB management: Skip IB

L0194: Special features:

First block in partition must be good

L0195: Comment:

exec

L0196: Partition 2

L0197: Partition start (in blocks): 000201 (0x00C9)

L0198: Partition end (in blocks): 000300 (0x012C)

L0199: Partition size (in blocks): 000000 (0x0000)

L0200: Partition max. allowed IB: 000016 (0x0010)

L0201: Partition IB management:

Check IB without Access

L0202: Special features:

First block in partition must be good

L0203: Comment:

res1

L0204: Partition 3

L0205: Partition start (in blocks): 000301 (0x012D)

L0206: Partition end (in blocks): 000400 (0x0190)

L0207: Partition size (in blocks): 000050 (0x0032)

L0208: Partition IB management:

Skip IB

L0209: Special features:

First block in partition must be good

L0210: Comment:

fsvs

L0211: Partition 4

L0212: Partition start (in blocks): 000401 (0x0191)

L0213: Partition end (in blocks): 000500 (0x01F4)

L0214: Partition size (in blocks): 000000 (0x0000)

L0215: Partition max. allowed IB: 000016 (0x0010)

L0216: Partition IB management:

Check IB without Access

L0217: Special features:

First block in partition must be good

L0218: Comment:

L0219: Partition 5

L0220: Partition start (in blocks): 000501 (0x01F5)

L0221: Partition end (in blocks): 001000 (0x03E8)

L0222: Partition size (in blocks): 000050 (0x0032)

L0223: Partition IB management: Skip IB

L0224: Special features:

None in use

L0225: Comment:

data

L0226: File loading successful.

```

Figure 15: Successful partition definition file load listing example in log window (an example from CSV format description was used).

Version 1.1/08.2021 Page 32 of 85

#### 7.1.9.1.4.1. Error codes on Partition definition file load

During the partition definition file loading, several errors can occur. Errors are always displayed in pg4uw log-window. Error message consists of error code and error description in the following form:

#### File loading problem!

#### Error code: #xxyy - error description

where xx stands for file format:

- 00 binary file

- 01 \*.mbn file containing just partition table

- 02 \*.mbn file containing both, partition table as well as partitions data

- 03 \*.csv file containing partition table

- 04 reserved for future use

- 05 \*.def file containing partition table

#### and yy stands for error type:

- 10 disk i/o error (disk i/o error, file access error, ...)

- 11 maximum buffer limit exceeded (file size grater than max. supported buffer size)

- 12 unable to re-allocate buffer (file size is grater than buffer size and there is some problem when reallocating the buffer (e.g. not enough disk space))

- 13 unknown separator (for \*.csv files, nor comma (,) nor semicolon (;) were detected as separator)

- 14 file does not specify any partition (none partition definition read)

- 15 too many partitions specified in file (max. 16 partitions are supported for Qualcomm Multiply Partition, max. 64 partitions generally)

- 16 incorrect numeric values format (typo in text-oriented files (\*.csv), e.g. @34 instead of 234)

- 17 version not supported (not supported version of algorithm specification detected)

- 18 invalid file header (damaged header, some mandatory item missing, ...)

#### 7.1.9.2. Access Method window options validity in partitioning mode

Only some of options available in **Access method window** are valid if invalid block management technique based on partitioning is applied. These are:

- Required Valid Blocks Area options

- Max. Allowed Number of Invalid Blocks in Device options

- Invalid Block Indication options (extended version)

- Tolerant verification options

- Special device features (if supported)

Please, see respective chapters for detailed informations.

Version 1.1/08.2021 Page 33 of 85

#### 7.1.9.3. SAFE WORKING PROCEDURE

- Select Multiple partitions with Skip IB in Access method window. It is very important to start with this selection, since it triggers programmer and control software internal pre-settings. Only after then it is safe to continue with next steps.

- 2. Prepare and load **Partition definition file**. In general, it does not matter what is loaded first partition definition file or input data image(s). But some customized implementations may pre-process input images with respect to specifications in partition definition file, so it is safer to familiarize with operation sequence as is listed here.

- 3. If necessary, set other options in **Access method window**, of those accepted in partitioning mode, see chapter **Access Method window options validity in partitioning mode**.

- 4. Load input data into buffer, see chapter **Access method window**.

- 5. Save your settings and data into project file and test the operation.

#### 7.1.10. LINUX MTD COMPATIBLE

This technique further extends **Multiple partitions with Skip IB** technique with a special feature used by MTD driver in Linux-based operating systems – Bad Blocks Table (BBT). All features and procedures mentioned in previous chapters dedicated to Multiple partitions with Skip IB technique are valid without any change. The difference is a new options group available in Access Method window and accepted only if this technique is in use – Linux MTD compatible options. Study, please, respective chapters to get complete information on how to use Linux MTD compatible technique.

#### Limitations:

Only Hamming ECC algorithm is supported by our programmers, see chapter ECC – Hamming (2×256 byte frame) variant 1 and 2. The algorithm can recover 1 bit error in 256 byte frame. If manufacturer prescribes more powerful error protection for target NAND flash device, Linux MTD compatible technique is not allowed for such device.

If you need to use another ECC algorithm, contact, please, our technical support with your demand.

See chapter Linux MTD compatible options for more information about available options.

## 7.1.11. REDIRECTION WITH HW LOOK UP TABLE (LUT)

This is a kind of redirection technique based on device internal hardware infrastructure. Once the block redirection link is created, it is permanent. New valid block is accessible while still addressing original invalid block.

The technique is available only for devices providing necessary hardware support. See your device datasheet for more information on this topic.

At time of this revision of the app-note release, we do not support HW-LUT for stacked (mutli-chip) devices.

Version 1.1/08.2021 Page 34 of 85

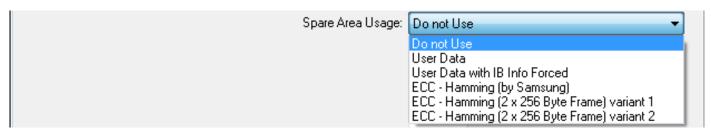

#### 7.2. Spare area usage

Our programmers support several modes of spare area usage. Any other spare area usage mode can be supported upon user's request.

Figure 16: Spare area usage options.

#### **7.2.1.** DO NOT USE

**Do not use** mode is about what its name means – spare area is not used. Data for spare area are neither expected in buffer (see Figure 4 in chapter **Loading data into pg4uw control software buffer**) nor programmed in or read from target device, respectively.

#### **7.2.2. USER DATA**

User data mode treats spare area as is, without any change. Spare area data are both, expected in buffer (see Figure 5 in chapter Loading data into pg4uw control software buffer) and programmed in or read from device, respectively.

This is default spare area usage mode for partitioning techniques (Multiple partitions with Skip IB and Linux MTD compatible).

#### Important note:

Using this mode may lead to block validity information loss if BI byte is rewritten with any data different from FFh (or FFFFh for x16 devices).

#### 7.2.3. USER DATA WITH IB INFO FORCED

This is an extension of **User data** mode. Data from buffer are modified during programming with aim to keep block validity information – the value at BI byte position is forced to FFh (or FFFFh for x16 devices).

User can change BI byte position from default using **Invalid Block Indication options (extended version)** and related settings.

Version 1.1/08.2021 Page 35 of 85

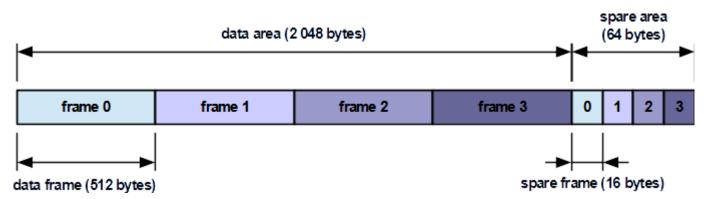

#### 7.2.4. ECC - HAMMING (BY SAMSUNG)

This spare area usage mode is based on Hamming ECC algorithm, as was proposed by Samsung some time ago. You can access original documents also from our archive: <u>256 byte frame</u>, <u>512 byte frame</u>

Using **ECC – Hamming (by Samsung)** mode, spare area data are not expected in buffer. Programmer will add spare data instead.

A page data area is segmented into 512 byte frames. Spare area is segmented into the same number of frames. E.g. for typical 2 048 + 64 byte page, data area will be segmented into 4 frames of 512 bytes, and spare area into corresponding 4 frames of 16 bytes each, see example on Figure 17.

Figure 17: ECC - Hamming (by Samsung) page segmentation example.

For each frame in data area, ECC checksum is calculated using Hamming algorithm. This algorithm is capable to detect up to 2 bit errors in a frame, and recover up to 1 bit error in a frame. The calculation produces 3 bytes of checksum. Calculated checksum is inserted into spare area, see Figure 18 and Figure 19 for layouts. Reserved bytes are not used and are left blank.

Figure 18: ECC Hamming (by Samsung) spare area layout for small page (512+16 bytes).

Figure 19: ECC Hamming (by Samsung) spare area layout for large page (2 048+64 bytes).

Version 1.1/08.2021 Page 36 of 85

On programming, ECC checksum is calculated and inserted into page buffer. Reserved bytes / words are kept blank. Checksums are programmed into device.

On verifying, ECC checksum is calculated from data in buffer and inserted into temporary internal compare page buffer. Device page is read as is and its spare area content is compared against calculated content in compare buffer.

On read, ECC checksum is calculated from read data and compared against checksum read from device. Detected errors are repaired before storage in buffer, if possible.

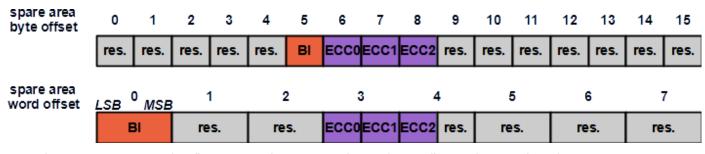

# 7.2.5. ECC - Hamming (2×256 BYTE FRAME) VARIANT 1 AND 2

This spare area usage mode is based on Hamming ECC algorithm, as is used in Linux MTD subsystem. It is the same spare area usage mode, as can be specified for **Linux MTD compatible** technique using **Apply MTD specific ECC on partition data** switch.

Using ECC Hamming (2×256 byte frame) mode, spare area data are not expected in buffer. Programmer will add spare data instead.

A page data area is segmented into 256 byte frames. Spare area is not segmented (compare to **ECC** – **Hamming (by Samsung)** mode).

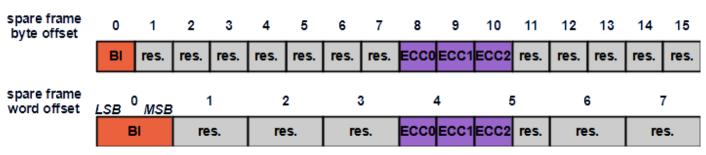

For each frame in data area, ECC checksum is calculated using Hamming algorithm. This algorithm is capable to detect up to 2 bit errors in a frame, and recover up to 1 bit error in a frame. The calculation produces 3 bytes of checksum. Calculated checksum is inserted into spare area, see Table 1 to Table 3 for layouts.

ECC Hamming (2×256 byte frame) **variant 1** to ECC Hamming (2×256 byte frame) **variant 2** difference is as follows:

In both cases, three bytes of checksum are calculated per data frame – ECC[0], ECC[1], ECC[2]. Variant 1 stores them in order ECC[0], ECC[1], ECC[2]. This corresponds to default layout used in Linux MTD driver. Variant 2 stores them in order ECC[1], ECC[0], ECC[2]. This corresponds to SmartMedia layout as can be specified for Linux MTD compatible technique by Use Smart Media bytes order for ECC switch (or by CONFIG\_MTD\_NAND\_ECC\_SMC switch in Linux MTD driver).

**On programming**, ECC checksum is calculated and inserted into page buffer. Reserved bytes / words are kept blank. Checksums are programmed into device.

**On verifying**, ECC checksum is calculated from data in buffer and inserted into temporary internal compare page buffer. Device page is read as is and its spare area content is compared against calculated content in compare buffer.

**On read**, ECC checksum is calculated from read data and compared against checksum read from device. Detected errors are repaired before storage in buffer, if possible.

Version 1.1/08.2021 Page 37 of 85

| Offset | Usage            |

|--------|------------------|

| 0      | Frame 0 – ECC[0] |

| 1      | Frame 0 – ECC[1] |

| 2      | Frame 0 – ECC[2] |

| 3      | Frame 1 – ECC[0] |

| 4      | Reserved         |

| 5      | Reserved         |

| 6      | Frame 1 – ECC[1] |

| 7      | Frame 1 – ECC[2] |

| 8 ~15  | Reserved         |

Table 1: ECC - Hamming (2x256 byte frame) variant 1 spare area layout for 512 + 16 byte page (variant 2 differs in ECC[0] - ECC[1] ordering).

| Offset | Usage            |

|--------|------------------|

| 0 ~ 39 | Reserved         |

| 40     | Frame 0 – ECC[0] |

| 41     | Frame 0 – ECC[1] |

| 42     | Frame 0 – ECC[2] |

| 43     | Frame 1 – ECC[0] |

| 44     | Frame 1 – ECC[1] |

| 45     | Frame 1 – ECC[2] |

| 46     | Frame 2 – ECC[0] |

| 47     | Frame 2 – ECC[1] |

| 48     | Frame 2 – ECC[2] |

| 49     | Frame 3 – ECC[0] |

| 50     | Frame 3 – ECC[1] |

| 51     | Frame 3 – ECC[2] |

| 52     | Frame 4 – ECC[0] |

| 53     | Frame 4 – ECC[1] |

| 54     | Frame 4 – ECC[2] |

| 55     | Frame 5 – ECC[0] |

| 56     | Frame 5 – ECC[1] |

| 57     | Frame 5 – ECC[2] |

| 58     | Frame 6 – ECC[0] |

| 59     | Frame 6 – ECC[1] |

| 60     | Frame 6 – ECC[2] |

| 61     | Frame 7 – ECC[0] |

| 62     | Frame 7 – ECC[1] |

| 63     | Frame 7 – ECC[2] |

Table 2: ECC - Hamming (2x256 byte frame) variant 1 spare area layout for 2 048 + 64 byte page (variant 2 differs in ECC[0] - ECC[1] ordering).

Version 1.1/08.2021 Page 38 of 85

| Offset           | Usage             |

|------------------|-------------------|

| 0 ~ 79           | Reserved          |

| 80               | Frame 0 – ECC[0]  |

| 81               | Frame 0 – ECC[1]  |

| 82               | Frame 0 – ECC[2]  |

| 83               | Frame 1 – ECC[0]  |

| 84               | Frame 1 – ECC[1]  |

| 85               | Frame 1 – ECC[2]  |

| 86               | Frame 2 – ECC[0]  |

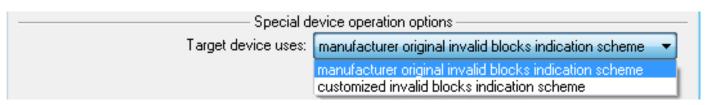

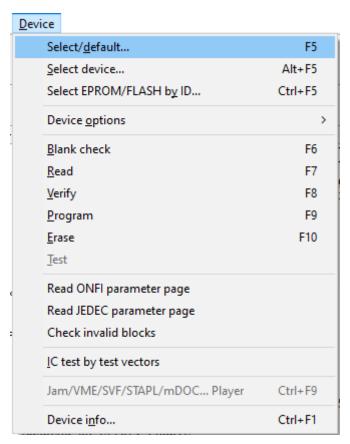

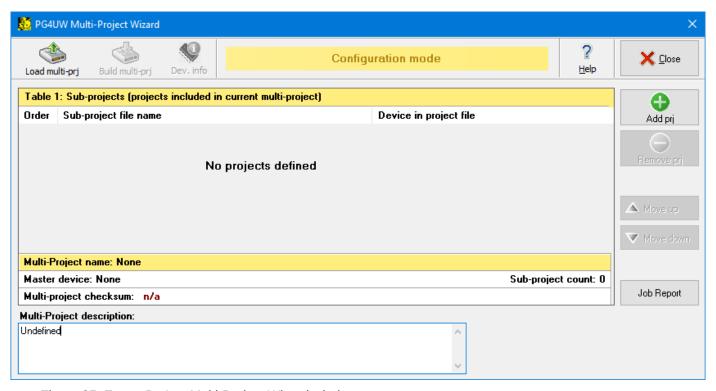

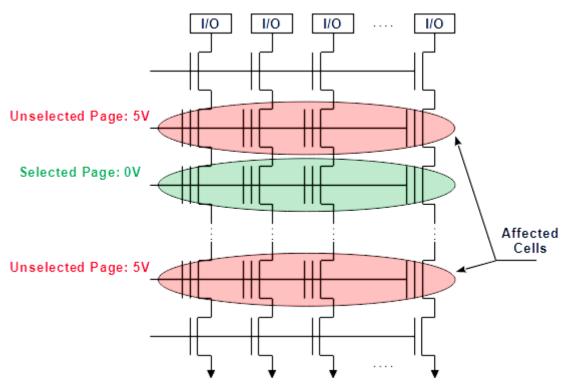

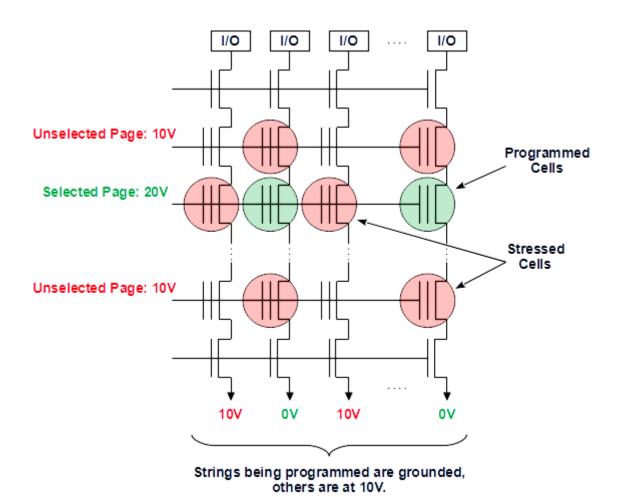

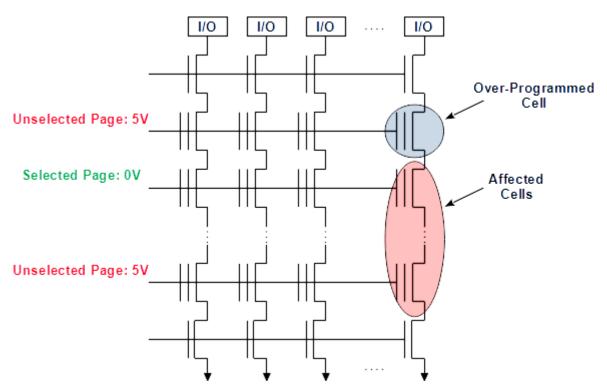

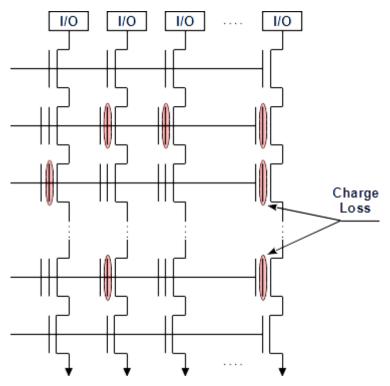

| 87               | Frame 2 – ECC[1]  |